離子注入高壓電源的注入雜質分布

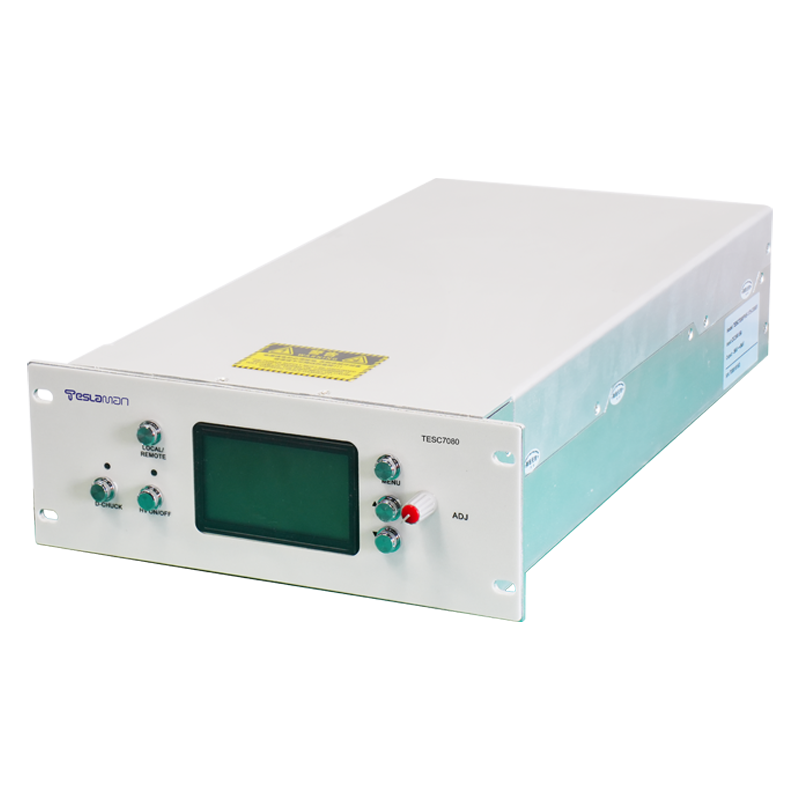

在半導體制造、材料表面改性等眾多領域,離子注入技術憑借其精確控制雜質引入的優(yōu)勢,成為關鍵工藝環(huán)節(jié)。而離子注入高壓電源作為這一技術的核心裝備,對注入雜質的分布起著決定性作用。

離子注入過程中,離子在高壓電源產(chǎn)生的強電場作用下被加速,獲得足夠動能后高速撞擊靶材表面并深入內部。高壓電源的輸出電壓和電流特性直接影響離子的加速效果,進而決定雜質的注入深度和分布情況。較高的電壓能賦予離子更大動能,使其穿透更深,在靶材內部形成較深的雜質分布;反之,較低電壓下離子注入深度較淺。而電流大小則影響單位時間內注入的離子數(shù)量,從而影響雜質濃度分布。

多種因素會干擾離子注入高壓電源實現(xiàn)理想的注入雜質分布。電源的穩(wěn)定性至關重要,若電壓或電流出現(xiàn)波動,離子的加速過程將不穩(wěn)定,導致雜質注入深度和濃度產(chǎn)生偏差。例如,電源內部電子元件老化、散熱不良等問題,都可能引發(fā)電壓紋波增大,使注入雜質在深度方向上的分布出現(xiàn)不均勻現(xiàn)象。此外,靶材的特性,如晶體結構、表面狀態(tài)等,也會對離子注入產(chǎn)生影響。不同晶體結構的靶材對離子的散射和阻擋作用不同,會改變離子的注入軌跡,導致雜質分布偏離預期。靶材表面的氧化層或污染物,可能阻礙離子的正常注入,影響雜質在表面區(qū)域的分布均勻性。

為實現(xiàn)精準且理想的注入雜質分布,需采取一系列針對性措施。在高壓電源設計方面,采用先進的穩(wěn)壓穩(wěn)流技術,如引入高精度反饋控制系統(tǒng),實時監(jiān)測并調整輸出電壓和電流,確保離子加速過程的穩(wěn)定性。通過優(yōu)化電源內部電路布局,減少電磁干擾,進一步提高電源的穩(wěn)定性。對于靶材,在離子注入前進行嚴格的預處理,如對表面進行拋光、清洗,去除氧化層和污染物,保證離子能夠順利注入。同時,根據(jù)靶材的晶體結構特性,調整離子注入的角度和能量,以優(yōu)化雜質分布。在實際生產(chǎn)中,還可利用計算機模擬技術,預先模擬不同電源參數(shù)和靶材條件下的雜質分布情況,為工藝參數(shù)的優(yōu)化提供依據(jù)。

精確控制離子注入高壓電源的注入雜質分布,在半導體芯片制造中意義重大。能夠實現(xiàn)雜質在特定區(qū)域的精確分布,有助于制造出性能更優(yōu)、集成度更高的芯片,滿足日益增長的電子產(chǎn)品小型化、高性能化需求。在材料表面改性領域,可根據(jù)材料的使用要求,精準控制雜質在表面層的分布,提升材料的耐磨、耐腐蝕等性能。

總之,離子注入高壓電源的注入雜質分布受多種因素影響,通過優(yōu)化電源設計、靶材處理以及借助模擬技術等手段,可實現(xiàn)對雜質分布的精確調控,為相關領域的技術發(fā)展提供有力支撐。